信号の立上りエッジまたは立下りエッジで割り込みを発生させ、ノイズ対策等の目的で

割り込み処理内で信号のレベルを再度確認する場合、以下の点に注意する必要があります。

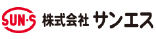

1.割り込み要因の信号と、ポートのレベルを読み取る信号が、CPU内で分岐している場合(例、H8 300H)

CPUによっては、割り込み要因はシュミットトリガー回路を通して処理され、

ポート読み取りはシュミットトリガー回路は通さずに値を読み取ることになります。

立上りの遅い信号や、ノイズがのりやすい信号の場合では、割り込み内でポートを読み取ったときに

割り込みを発生したときと High/Lowのレベルが異なる可能性があります。

下図の(A)のタイミングで割り込みを発生し、割り込み処理が開始されて(B)の時間帯で

割り込み処理のポートレベルの判定処理を行うと、(B)時間帯では、信号レベルが

”ポート読み取り値の閾値”より小さいので”Low”レベルを検知することになります。

したがって、割り込み内では、処理を行わず割り込みを終了してしまうことになります。

その後、信号レベルは割り込みレベルのLowのレベルまで下がらない((C)の区間)ので、

割り込みは発生せず、割り込み処理が1回分実行しないことになってしまいます。

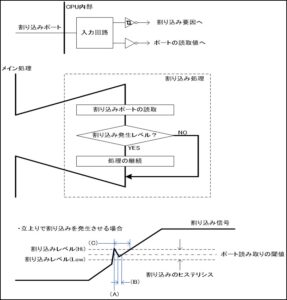

2.割り込み要求フラグのクリアタイミングとポートレベルの確認タイミングによる不具合の可能性

前記のように割り込み要因とポート読み取りの回路が分岐していない回路でも、

処理のタイミングによっては同様の問題が発生する可能性があります。

下図の(A)の時点で割り込み発生し、(B)~(C)の時点で割り込み信号のレベルの判定を行って

割り込み信号がLowだと割り込み内の処理を行わずに、(C)のタイミングより後で割り込み要求フラグを

クリアするようなタイミングになった場合、割り込み処理は実行されないことになります。

これを回避するには、(C)のタイミングより前に割り込み要求フラグをクリアする必要があります。

※補足

両エッジ割り込みを設定し、割り込み処理内でHighかLowを判定する場合も

上記同様の不具合が発生する可能性があるので、十分検証する必要があります。